ISSN: 2356-5608, Vol.3, issue 3 Copyright IPCO-2015-pp.17-20

# CMOS Sensor Technology and SPICE Simulation of Sensing Circuits

Ruoyan Gu<sup>1</sup>, Kopal Kulshreshtha<sup>2</sup>, Qing K. Zhu<sup>3</sup>

International Technology University 2711 N 1<sup>st</sup> Street, San Jose, CA 95134

¹ruoyan.gu@itu.edu ²kopal.kulshreshtha@itu.edu ³qzhu@itu.edu

Abstract— This paper describes a VLSI design project on CMOS image sensor chips. It shows architecture, colour filter mosaic array, active pixel sensor photodiodes, photodiode APS, sampling circuit and voltage-current conversion circuits. A simplified circuit structure and SPICE simulations have been done for sensing circuit. A single-stage OTA (Operational Transconductance Amplifier) design is also described and simulated for low voltage sigma-delta ADC applications.

*Keywords*— CMOS image chip, DSM, sensing, current-voltage conversion, circuit, Sigma-Delta ADC, OTA, low-voltage, low power, SPICE simulation.

## I. INTRODUCTION

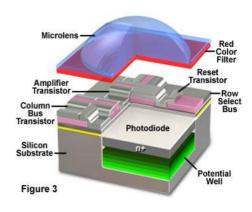

An image sensor is a device that converts an optical image into electronical signal. It is used mostly in digital cameras, smart phones, camera modules and imaging devices. It contains a bayer colour filter mosaic array and underlying active pixel sensor photodiodes. It also contains analog-to-digital conversion, analog signal processing, clock and timing control. Digital logic circuits include interface, timing, processing and data output. Fig. 1 shows underlying CMOS active pixel sensor (APS) photodiode structure in CMOS image chip [1]. It contains photodiode on silicon substrate and potential well. It also contains column and row select buses, reset transistor, amplifier transistor, microlens and red colour filters.

Major advantage of CMOS image sensor is to integrate processing and control functions directly in VLSI technology. Active pixel sensor (APS) architecture includes both photodiode and read amplifier in each pixel. This will enable charges accumulated by photodiodeto be converted and amplified intovoltages in the pixel. Voltages arethen transferred through rows and columns to signal-processing unit. Among different ADCs, sigma-delta ADC is the most suitable for high-resolution applications due to higher linearity, which is achieved by using linear quantizer and oversampling technique. However, non-idealities in building blocks still strongly affect ADC output performance. Scaling of CMOS technology makes non-idealities even more severe. The most important constraint is the distortion problem in high-resolution sigma-delta ADCs. The continually decreased supply

voltage in low-power applications results inmore performance degradation[1].

Fig. 1APS (Active Pixel Sensor) Photodiode Structure [1].

This paper is organized in the following sections. Section I is the introduction about image sensor CMOS technology. Section II describes APS (active pixel sensor) and sampling circuits. Section III presents SPICE simulation results on sensing circuit. Section IV describes a single-stage OTA (Operational Transconductance Amplifier) design and Spectre simulations are reported for AC, DC and transient analyses. Section V gives conclusions and future Internet applications using image sensor chips.

#### II. APS AND SAMPLING CIRCUIT

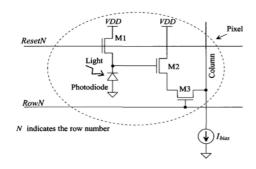

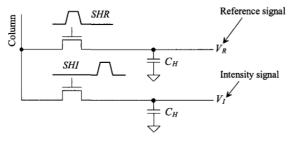

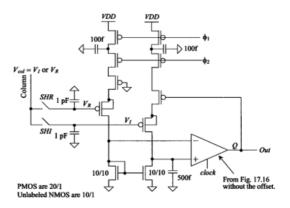

In sigma-delta modulation CMOS imager, analog signals from APS photodiodes are sensed to DSM sensing circuits. Outputs from DSM sensing circuits go thorough digital counters to output digital codes. Fig. 2 shows APS sampling schematic. Device M1 works as reset switch. M2 is a source follower. M3 performs as row select switch. A currentsource is used to discharge parasitic capacitance. When ResetN and RowN are high, pixel reference voltage VR is placed on column line as shown in Fig. 3. At this time sample and hold reference signal, SHR, goes high and VR is sampled onto a hold capacitor as shown in Fig. 3. In the next state, ResetN goes low and photodiode changes the light into charges. After

ISSN: 2356-5608, Vol.3, issue 3

# Copyright IPCO-2015-pp.17-20

the aperture time, the information from photodiode is on the column line. VI is then sampled and held on a held capacitor when signal SHI goes high.

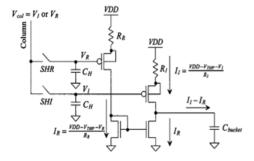

Fig. 4 shows the schematics of current conversion and subtracting circuits. We take difference of currents according to a current mirror. The current corresponding to reference voltage is calculated as follows:

$$I_R = \frac{VDD - V_{THP} - V_R}{R_R} = \frac{V_{R,shift}}{R_R}$$

The current corresponding to intensity of the light is calculated as follows:

$$I_{I} = \frac{VDD - V_{THP} - V_{I}}{R_{I}} = \frac{V_{I,shift}}{R_{I}}$$

So difference in these currents is summed in the bucket capacitor.

Fig. 2 APS Sampling

Fig. 3Reference and Intensity Signals.

Fig. 4 Current Conversion and Subtracting Circuits.

## III. SENSING CIRCUIT AND SIMULATION

Fig. 5 shows sensing circuit used in CMOS image chip. We use Spice circuit simulation tool to simulate the sensing circuit.  $V_{\rm I}$  and  $V_{\rm R}$  are varied in simulations to observe the stability of output signals. The circuit is able to sense about 500ns in voltages  $V_{\rm I}$  and  $V_{\rm R}$  based on simulation waveforms.Table I lists simulation results with three  $V_{\rm I}$  voltages in the following equations:

$$V_{I, shift} = VDD - V_{THP} - V_{I};$$

$V_{R, shift} = VDD - V_{THP} - V_{R}.$

Fig. 5SignalsSensing Circuit.

$\label{eq:table_interpolation} \textbf{TABLE I}$  Simulation Results of Sensing Circuit.

|                        | Simulation I | Simulation II | Simulation III |

|------------------------|--------------|---------------|----------------|

| $V_I$                  | 650mV        | 645mV         | 400mV          |

| $V_R$                  | 650mV        | 650mV         | 650mV          |

| V <sub>I</sub> , shift | 100mV        | 105mV         | 357mV          |

| V <sub>R</sub> , shift | 100mV        | 100mV         | 100mV          |

## IV. SIGNLE-STAGE OTA DESIGN

Being the most important building block in analog sensing circuits, the amplifier faces difficulty in the low-voltage design, providing high gain and reasonable output swing while for low-power consumption. The intrinsic gain of the transistor is usually lower than 20dB. A usual way to boost the gain, cascoding of transistors, is not available in low-voltage design due to its output swing limitation. Alternatively, cascading transistor, i.e. the multi-stage amplifier, is possibly adopted. However, a cascade structure, which boosts gain with more than one amplifying stage, normally increases the power consumption and needs the frequency compensation. These constraints lead to the most power efficient solutionsingle-stage amplifier without cascading in our investigation.

ISSN: 2356-5608, Vol.3, issue 3

Copyright IPCO-2015-pp.17-20

Specifications of the sigma delta ADC for which OTA has been designed aregiven as follows. The dynamic rangeDR = 65 dB; input frequency: 10 kHz; ADC sampling rate: Fs = 20 KHz and maximum voltage: 1.2V in a 130nm process library. Based on the dynamic range, ADC resolution can be calculated as (DR - 1.76)/6.02 = 11 bits. Number of ADC quantization levels is required as  $2^{(Resolution of ADC)} = 2048$ , OSR = 32, sample time  $1/(Fs^{(Resolution of ADC)}) = 32*20$  KHz or 640 KHz.

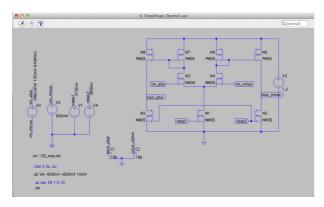

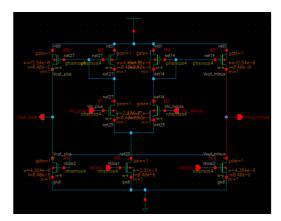

Another sigma-delta ADC design perspective is that the gain of OP amplifier should be higher than OSR. GBW (Gain Bandwidth Product) should be higher than product of OSR and ADC sampling frequency. The gain requirement is not very high in our design, since OSR is only 32. Single-stage current mirror OTA (Operational Transconductance Amplifier) fulfils the above requirements and makes it a good candidate for low-power low-voltage amplifier design [2]. There is no need to go for multi-stage OTAs and also no compensation is needed. The schematic of the single-stage OTA design is shown in Fig. 6.

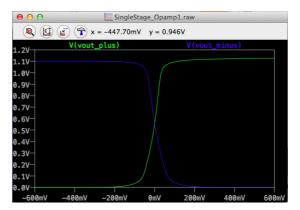

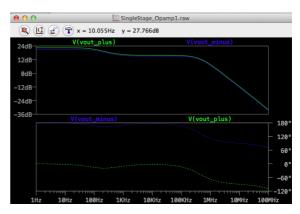

Fig. 7 shows DC analysis of the OTA design. The offset of OTA was set to 600mV i.e. half of full voltage range allowed in the design. AC analysis showed the gain of OP Amp is around 30, which is pretty close to OSR value 32 as shown in Fig. 8. The bandwidth was found around 2.3 MHz which was well above 32\*20KHz = 640KHz requirement. The phase margin was 83 degrees. Hence, this OTA design was found to be satisfactory.

Fig. 6 One-Stage OTA Schematic.

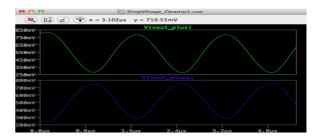

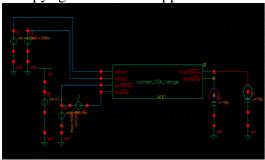

Fig. 9 shows the transient analysis simulationresult. For input sine wave amplitude, amp =100 mV, output is a perfect sine wave; for amp = 150 mV, output has a minor distortion at the peak; for amp = 250 mV, output still has a sine format, and for amp > 250 mV, the distortion increases. Fig. 10 shows the schematic of OTA. Fig. 11 shows the setup made to simulate OTA. Table 2 shows rise/fall time based on simulations. It works for the input frequency 640 KHz. The single stage current mirror OTA is satisfactory for low-voltage sigma-delta ADC applications.

Fig. 7 DC Simulation.

Fig. 8 AC Simulation.

Fig. 9 Transition Analysis.

Fig. 10 OTA Schematic.

ISSN: 2356-5608, Vol.3, issue 3 Copyright IPCO-2015-pp.17-20

Fig. 11OTA Stimulus Setup.

TABLE II

RISE/FALL TIME OF OTA OUTPUTS.

|           | Vout_plus | Vout_minus |

|-----------|-----------|------------|

| Rise time | 293.54ns  | 328.85ns   |

| Fall time | 264.56ns  | 287.20ns   |

## V. CONCLUSIONS AND APPLICATIONS

CMOS image sensor chip technology becomes popular due to continued integration in the CMOS process. In this paper, we describe a CMOS image sensorproject. It shows architecture, colour filter mosaic array, active pixel sensor photodiodes, photodiode APS, sampling circuit and voltage-current conversion circuits. Simplified circuits and SPICE simulations have been done for sensing circuit. Single-stage OTA (Operational Transconductance Amplifier) is described and Spectre simulations are reported for AC, DC and transient analyses. Performance and stability are satisfactory for low-voltage sigma-delta ADC design. Among different analogue-to-digital (ADC) converters, sigma-delta ADC is the most suitable for high-resolution applications. Main efforts are optimizing non-idealities in the sigma-delta ADC circuit.

Many technically challenging issuesstill remain to apply CMOS image chips in low-power, high-density and low-cost applications. Photodiodes and detectors are key to improve the resolution, accuracy, size and low-cost integration in image chips. Triple-well photodiodes technology can reduce leakage current and improve the stability [11]. Other techniques including dual-Vt, dual-oxide-thickness devices as well as Fin FET transistors are used to reduce the leakage current especially in mobile applications [12].

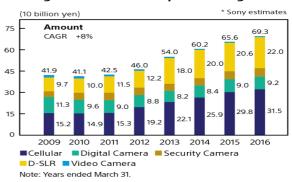

CMOS image chips are in the strong demand for Internet applications, as shown in Fig. 12. For example, we can build smart city environment with the following Internet-and-sensor applications [13]:

- Smart parking to monitor parking spaces available.

- *Noise maps* to monitor sounds in city.

- Electromagnetic field levels to detect energy radiated in cells and WIFI routes.

- Smart helath to detect available health cares and hospital facilities.

- Smart lighting to use intelligent and weather adaptive lighting in streets and areas.

- Waste management to detect rubbish levels in containers.

- Smart traffic to detect routes, congestions, climate conditions and unexpected events such as accidents and traffic jamson roads.

#### **Image Sensor Market by Main Usage**

Fig. 12 MarketGrowth of Image Sensor Chips.

#### REFERENCES

- [1] R. Turchetta, K. R. Spring, M. W. Davidson, "Introduction to CMOS image sensors", Application notes, Molecular Expressions, 2004.

- [2] L. Yao, M. Steyaert and W. Sansen, "Low-power low-voltage sigmadelta modulators in nanometer CMOS", 2006.

- [3] S. Taranovich, "Integrated CMOS image sensor architecture: the analog camera", Planet Analog, 2013.

- [4] C. Hu-Guo, etc. "CMOS pixel sensor development: a fast read-out architecture with integrated zero suppression", Journal of Instrumentation, Vol. 4, April 2009.

- [5] S. Mendis, S. Kemeny, R. Gee, B. Pain, C. Staller, Q. Kim, and E. Fossum, "CMOS active pixel image sensors for highly integrated imaging systems", IEEE J. Solid-State Circuits, Vol. 32, pp. 187-197, 1997.

- [6] N. Akahane, S. Sugawa, S. Adachi, K. Mori, T. Ishiyuki, and K. Mizobuchi, "A sensitivity and linearity improvement of a 100-dB dynamic range CMOS image sensor using a lateral overflow integration capacitor",

- [7] IEEE J. Solid-State Circuits, Vol. 41, pp. 851-858, Apr. 2006.

- [8] P. Dudek, "Adaptive sensing and image processing with a general-purpose pixel-parallel sensor/processor array integrated circuit", International Workshop on Computer Architecture for Machine Perception and Sensing, 2006.

- [9] B. P. Brandt, D. E. Wingard, B. A. Wooley, "Second-order sigma-delta modulation for digital-audio signal acquisition", IEEE J. Solid-State Circuits, Vol. 26, pp. 618-627, Apr. 1991.

- [10] B. E. Boser, B. A. Wooley, "The design of sigma-delta modulation analog-to-digital converters", IEEE J. Solid-State Circuits, Vol. 23, pp. 1298-1308, Dec. 1988.

- [11] B. Nakhkoob B, S. Ray, M.M. Hella, "High speed photodiodes in standard nanometer scale CMOS technology: a comparative study", Optics Express, Vol. 20, Issue 10, pp. 11256-11270, 2012.

- [12] S. K. Hadia, R. R. Patel, Y. P. Kosta, "FinFET Architecture Analysis and Fabrication Mechanism", International Journal of Computer Science Issues, Vol. 8, Issue 5, pp. 235-240, Sep 2011.

- [13] "50 sensor applications for a smarter world", www.libelium.com, 2014.